TrellisWare F-LDPC FEC Прямая коррекция ошибок

Код с низкой (меняющейся) плотностью проверок на чётность (F-LDPC) компании TrellisWare

Компания TrellisWare разработала семейство F-LDPC кодов в ответ на повсеместное требование высокопроизводительных функций прямого исправления ошибок (FEC) в различных коммерческих и военных приложениях. Коды F-LDPC предлагают уровень производительности, приближающийся к емкости, при любых скоростях кода и типах модуляции, без потери параметров задержки или пропускной способности декодера.

Мы предлагаем коды F-LDPC в качестве ядра для FPGA и ASIC устройств. Стандартное ядро поддерживает 8 размеров блоков, 40 значений скорости кода, 4 типа модуляции и может быть мгновенно перенастроено. При этом не потребуется жертвовать задержкой при переходе от декодирования 128 разрядного, скорость-1/2, QPSK-модулированного блока данных к блоку данных 16QAM-модуляции в 16384 разряда, скорость 32/33.

Компания TrellisWare может добавить размеры блоков и скорости кода, необходимые заказчику, до или после поставки, в качестве обновления в программируемом ПЗУ.

Коды F-LDPC используются на терминалах с очень малой апертурой (VSAT), средствах оптической связи свободного пространства (FSO), голографических системах хранения, военных формах сигнала и собственных продуктах компании TrellisWare для тактической мобильной одноранговой сети (MANET). Некоторые потребители ценят F-LDPC за показатели пропускной способности (Гбит/с) в FPGA, тогда как другие считают главным простоту его внедрения. Кроме этого, гибкость F-LDPC дает преимущество при разработке новых форм сигнала или реализации обратной совместимости с традиционными каналами связи.

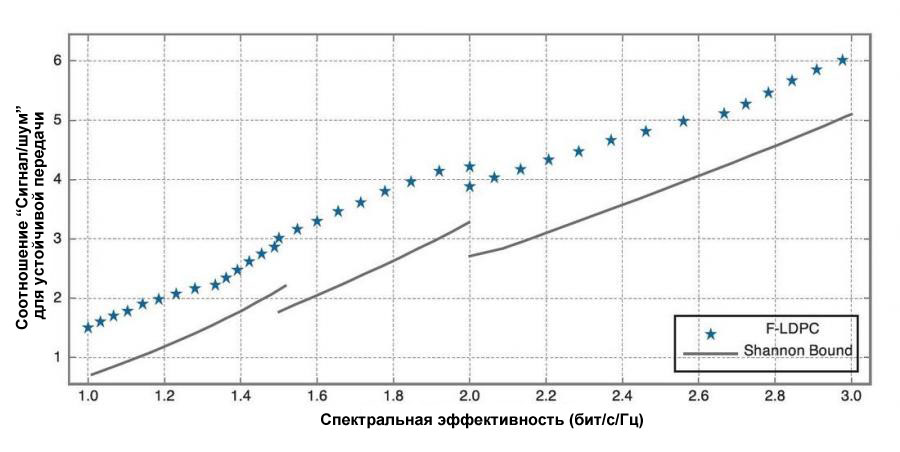

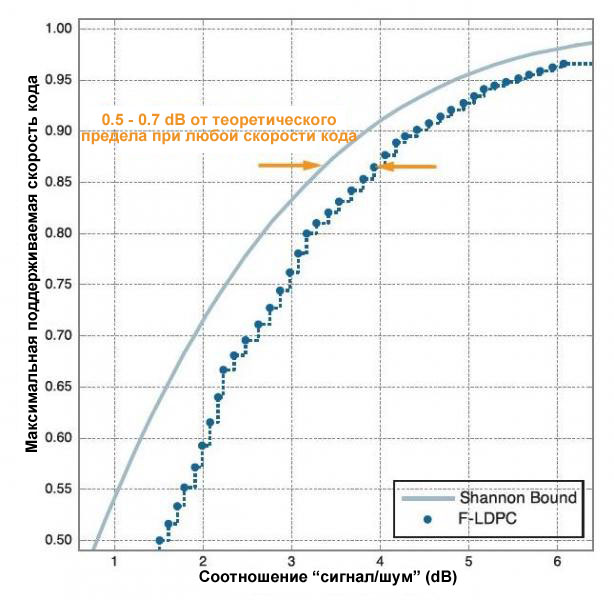

Код F-LDPC предлагает рабочие характеристики в пределах 1 dB от теоретических границ при любых скоростях кода и типах модуляции. Это достигается за счет применения простой архитектуры декодирования с высокой пропускной способностью.

Отличные показатели производительности F-LDPC по емкости и порогам делают его привлекательным для пользователей различных рынков и приложений:

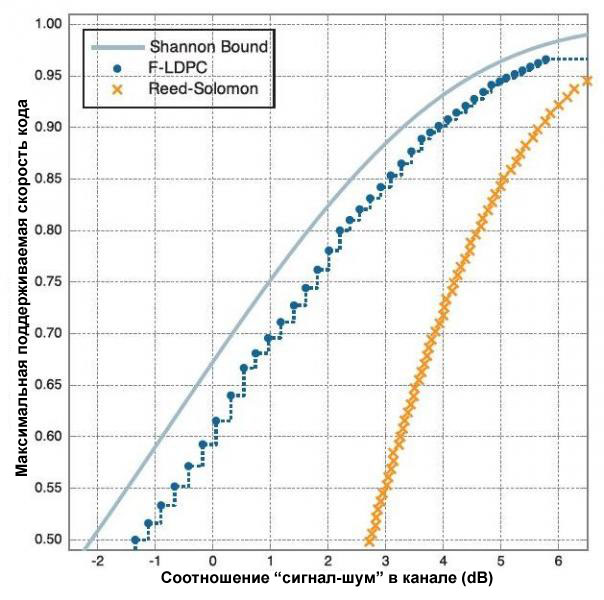

- Замена Viterbi/Reed Solomon FEC на современный код без изменения других элементов формирования сигнала

- Использование в бюджетных VSAT и M2M каналах связи

- Разработчики оптических каналов связи и E диапазоны используют преимущества современных кодов для повышения пропускной способности до нескольких гигабит в секунду

|  |

Функциональные особенности

НЕПРЕВЗОЙДЕННАЯ ГИБКОСТЬ

- Единственно ядро кодера/декодера поддерживает 40 скоростей кодового потока (1/2-32/33) и несколько размеров блоков. По умолчанию размеры блоков следующие: 128, 256, 512, …, 16384 бит

- Единственно ядро кодера/декодера поддерживает любые комбинации размеров блоков, скоростей обмена данными и типов модуляции

- Конфигурация в режиме реального времени: Изменение размера блоков не вносит задержку

- К стандартному ядру могут быть добавлены специфичные размеры блоков и скорости кодового потока

ПОДТВЕРЖДЕННАЯ ПРОИЗВОДИТЕЛЬНОСТЬ

- Предельно возможные рабочие характеристики с низкой сложностью внедрения; максимальный процент успешно переданных сообщений (MCR)

- Минимальный уровень ошибок

- Высокие эксплуатационные характеристики для небольших размеров блоков

ВЫСОКАЯ ПРОПУСКНАЯ СПОСОБНОСТЬ, НИЗКАЯ-СЛОЖНОСТЬ

- Пропускная способность до 10 Гбит/с в одной FPGA

- Возможная пропускная способность до 100 Гбит/с в ASIC

- Уровень сложности существенно ниже, чем в LDPC и турбо кодах